Bolt Graphics Tapes Out Zeus GPU Test Chip on TSMC 12nm, Claims 17x Lower Compute Cost

Introduction

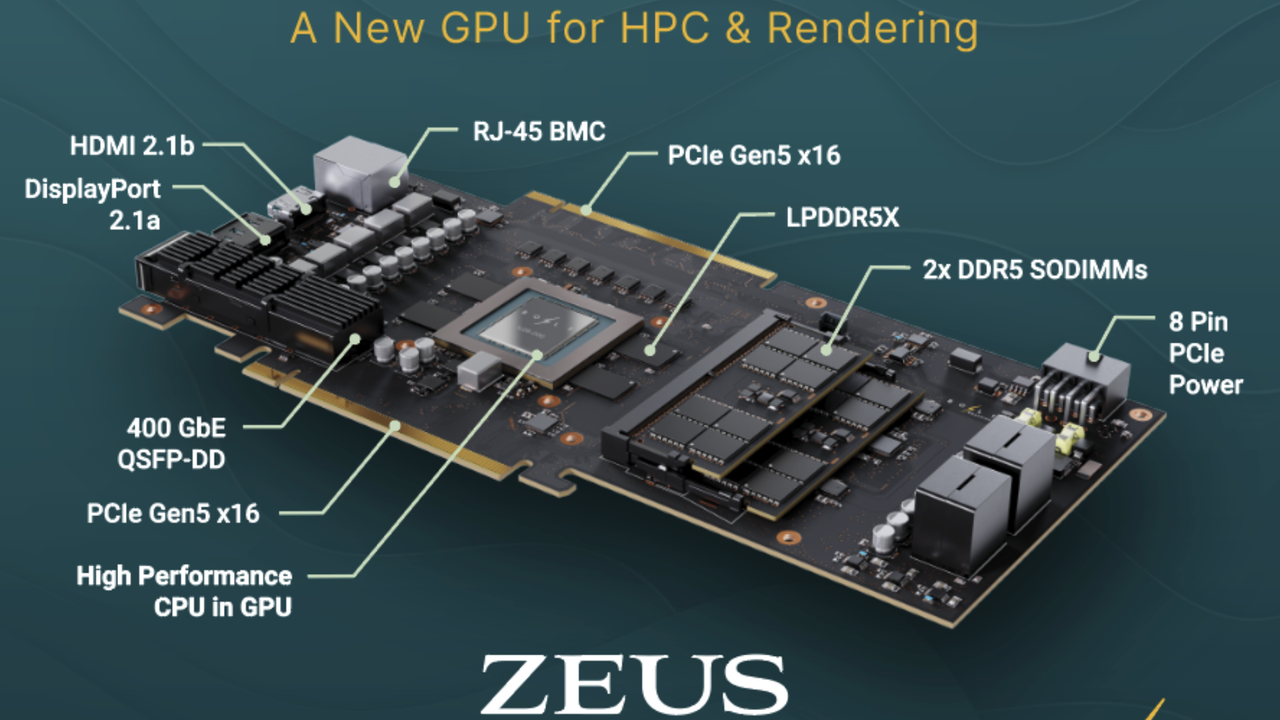

Bolt Graphics, a new entrant in the artificial intelligence hardware landscape, has announced a significant step in its development journey. The company has completed the "tape-out" of its first GPU test chip, named Zeus 1c26-032. This prototype was manufactured using TSMC's 12-nanometer production process, a clear indication of the company's strategic approach.

The most notable detail from the announcement is Bolt Graphics' claim: the Zeus chip promises to offer up to a 17x lower cost of compute compared to current solutions. While this is a claim for a test chip, this potential saving could have profound implications for companies looking to optimize the costs of their AI workloads, particularly for on-premise deployments.

Technical Details and Production Context

"Tape-out" represents a crucial phase in semiconductor development, indicating that the chip's design has been finalized and sent to the foundry for physical production. In this case, the choice of TSMC and its 12-nanometer process is noteworthy. The 12nm node is a mature and established technology, offering a balance between production costs and performance, distinguishing itself from more cutting-edge (and expensive) processes like 5nm or 3nm.

This decision could be strategic for Bolt Graphics, allowing them to contain development and production costs for a first test chip, and potentially contributing to the promise of reduced compute cost. However, the company has not yet released detailed specifications regarding VRAM, throughput, or latency, which are fundamental parameters for evaluating the effectiveness of the Zeus chip in Large Language Model (LLM) inference or training scenarios.

Implications for On-Premise Deployments

The emergence of new hardware providers like Bolt Graphics is particularly relevant for organizations evaluating on-premise or self-hosted deployments for their AI workloads. The promise of a drastically lower cost of compute, if realized, could significantly alter the Total Cost of Ownership (TCO) for local AI infrastructures. Companies, especially those with stringent data sovereignty, compliance requirements, or operating in air-gapped environments, are constantly seeking cost-effective alternatives to cloud offerings.

A hardware offering that reduces the cost per unit of compute can make on-premise deployments even more competitive, allowing AI operations to scale while maintaining full control over data and infrastructure. For those evaluating on-premise deployments, complex trade-offs exist that AI-RADAR analyzes in detail, offering analytical frameworks on /llm-onpremise to support decisions related to CapEx, OpEx, and performance.

Future Outlook and Challenges

It is crucial to emphasize that the Zeus 1c26-032 is, for now, a test chip. The journey from the "tape-out" phase to mass commercialization is long and fraught with challenges. Bolt Graphics will not only need to validate its cost and performance claims through independent benchmarks but also build a robust software ecosystem, including drivers, libraries, and integrations with major machine learning frameworks.

Competition in the AI hardware acceleration sector is intense, dominated by established players. However, the introduction of new architectures promising significant efficiencies can stimulate innovation and offer more choice to technical decision-makers. Bolt Graphics' success will depend on its ability to transform initial promises into concrete, competitive products capable of meeting the performance and cost demands of the rapidly evolving AI market.

💬 Comments (0)

🔒 Log in or register to comment on articles.

No comments yet. Be the first to comment!