Innovation in the 18A Manufacturing Process

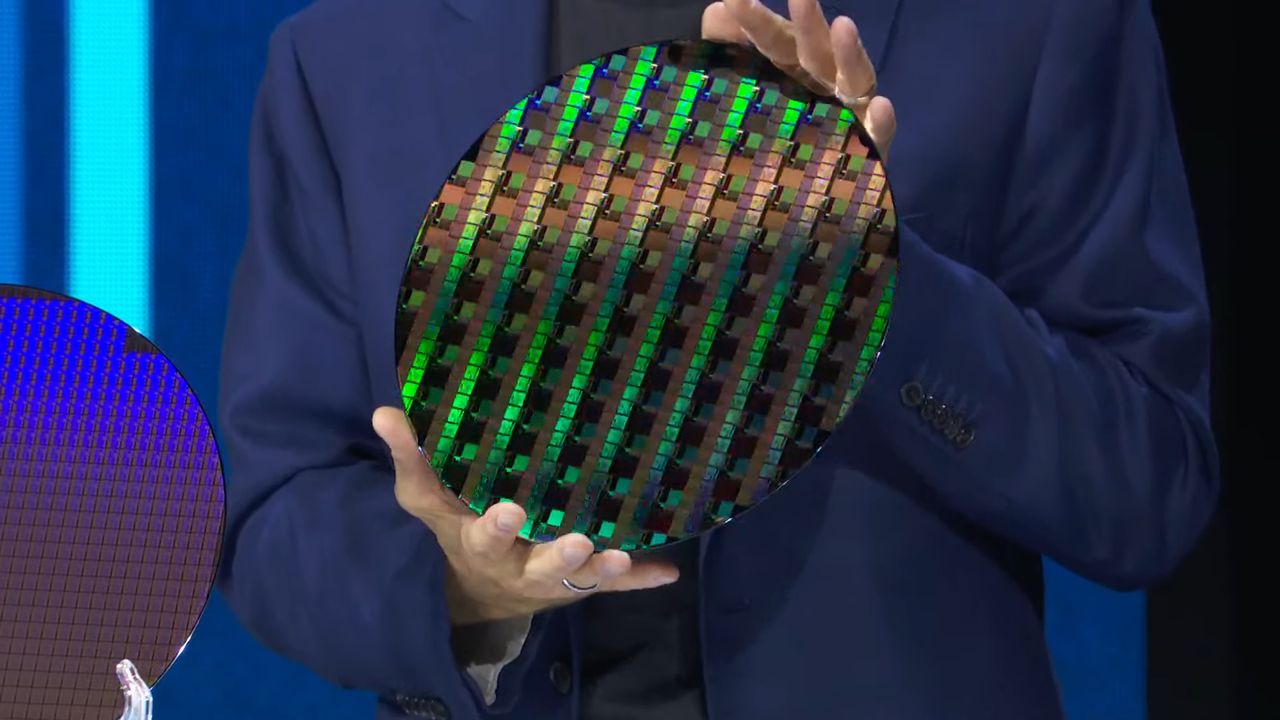

Intel is demonstrating significant progress in its 18A manufacturing process, a crucial technological node for the next generation of chips. Recent market analyses highlight how the company is managing to extract more value from each individual wafer. This achievement is attributed to a targeted strategy for yield optimization, which includes focusing on the peripheral areas of the wafer, traditionally more complex to manage.

Reducing yield variability across the entire wafer surface is a decisive factor. In the past, imperfections or deviations in specifications could compromise entire sections, reducing the number of functional chips. By improving the uniformity of the manufacturing process, Intel is able to convert a higher percentage of raw silicio into sellable CPUs, thus maximizing the investment in each fabrication cycle.

Technical Details and Production Challenges

The 18A node represents a leap forward in transistor miniaturization and efficiency. Producing chips at such advanced nodes involves immense challenges, from Extreme Ultraviolet (EUV) lithography to managing impurities at an atomic level. Intel's approach, focused on optimizing wafer edges, suggests a refinement of exposure, deposition, and etching techniques that minimize defects even in the outermost areas, where tolerances are often harder to maintain.

This improvement in yield is not just a matter of quantity, but also of quality. Lower variability implies that the produced chips are more consistent in terms of performance and power consumption, fundamental aspects for enterprise customers. The ability to produce a greater number of reliable CPUs from each wafer has a direct impact on the supply chain and the availability of critical components for the global technological infrastructure.

Implications for On-Premise Deployments and TCO

The increased availability of advanced CPUs, resulting from improved production yield, has significant implications for organizations planning on-premise deployments. A more stable and predictable supply of cutting-edge hardware allows CTOs and infrastructure architects to plan data center expansion with greater certainty, especially for intensive workloads such as Large Language Model (LLM) Inference and training.

From a Total Cost of Ownership (TCO) perspective, greater efficiency in chip production can translate into better accessibility of components, influencing acquisition costs and potentially reducing hardware waiting times. This is crucial for companies prioritizing data sovereignty and direct control over infrastructure, opting for self-hosted or air-gapped solutions. For those evaluating on-premise deployments, AI-RADAR offers analytical frameworks on /llm-onpremise to assess the trade-offs between costs, performance, and control.

Future Outlook in the Semiconductor Industry

Intel's progress in the 18A node underscores the intensity of competition in the semiconductor industry and the strategic importance of innovation in manufacturing processes. The ability to improve wafer yield not only strengthens the company's competitive position but also helps meet the growing global demand for computing power.

As the industry continues to push the limits of Moore's Law, attention to micro-optimization of every stage of the production process will become increasingly critical. These developments not only ensure greater economic efficiency for manufacturers but also ensure that the global technological ecosystem can rely on a constant flow of increasingly performant and reliable components, essential for the advancement of artificial intelligence and other emerging technologies.

💬 Comments (0)

🔒 Log in or register to comment on articles.

No comments yet. Be the first to comment!