Google Redefines TPU Architecture with a Dual Approach

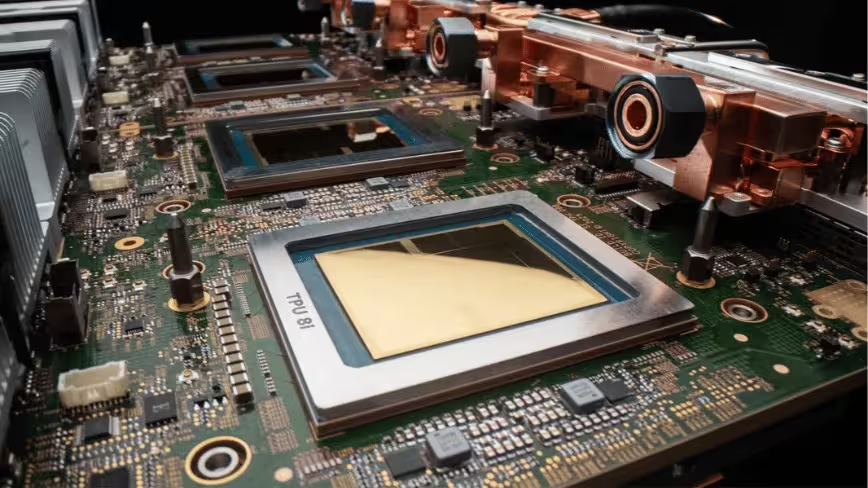

Google recently announced a significant evolution in its strategy for Tensor Processing Units (TPUs), the processing units dedicated to artificial intelligence. During the Cloud Next 2026 event, the company made its seventh-generation TPU, named Ironwood, generally available and simultaneously offered a preview of its eighth-generation architecture. The latter introduces a fundamental distinction: two separate chips, the TPU 8t (Sunfish) for model training and the TPU 8i (Zebrafish) for inference.

This move marks a turning point in AI chip design philosophy, highlighting increasing specialization to optimize performance based on specific workloads. The seventh generation, Ironwood, already demonstrates remarkable capabilities, reaching 4.6 petaFLOPS per single chip and scaling up to 42.5 exaFLOPS in a superpod configuration consisting of 9,216 chips. Such figures underscore Google's commitment to providing high computing power for the most complex AI needs.

Hardware Specialization: Dedicated Chips for Training and Inference

The introduction of TPU 8t and 8i represents a clear direction towards hardware specialization. The TPU 8t, designed by Broadcom, will be optimized for the intense and prolonged training operations of Large Language Models (LLM) and other AI models. These activities require high floating-point computing capacity and efficient memory management for large datasets. Conversely, the TPU 8i, developed by MediaTek, will focus on inference, which is the execution of trained models to generate predictions or responses. Inference workloads often benefit from high throughput and low latency, with particular attention to energy efficiency and the ability to handle variable batch sizes.

Both eighth-generation chips aim to leverage TSMC's 2nm manufacturing process, a cutting-edge technology that promises higher transistor density and improvements in energy efficiency and performance. The availability of these new architectures is anticipated for late 2027, suggesting a timeframe within which companies can evaluate the integration of these solutions into their infrastructures.

Implications for On-Premise Deployments and Data Sovereignty

The differentiation between training and inference chips has significant implications for companies considering on-premise deployments or hybrid solutions. The choice of dedicated hardware allows for more precise resource optimization, potentially reducing the Total Cost of Ownership (TCO) for specific workloads. For example, a company primarily performing inference might opt for a larger number of TPU 8i units, optimizing operational costs and energy efficiency compared to a more generic architecture.

For organizations with stringent data sovereignty requirements, compliance, or those operating in air-gapped environments, the availability of specialized hardware offers greater flexibility in designing local stacks. The ability to choose specific components for their training or inference needs can facilitate the creation of robust and controlled AI infrastructures, reducing reliance on external cloud services for the most sensitive operations. AI-RADAR offers analytical frameworks on /llm-onpremise to evaluate the trade-offs between different deployment strategies.

The Future of the AI Chip War: A Matter of Design Philosophy

Google's decision to split its TPU architectures into dedicated units for training and inference is not just a technical move but reflects a broader "design philosophy fight" in the AI chip sector. While some market players focus on more general-purpose architectures or solutions that try to balance both workloads, Google seems to be betting on extreme specialization to maximize efficiency and performance in specific use cases.

This strategy could lead to more performant and cost-effective solutions for certain applications, but it might also introduce complexity in infrastructure management for those requiring flexibility between training and inference on the same hardware. The AI chip market continues to evolve rapidly, and Google's approach with the TPU 8t and 8i will be a key factor to observe in understanding the future directions of hardware innovation in artificial intelligence.

💬 Comments (0)

🔒 Log in or register to comment on articles.

No comments yet. Be the first to comment!